(内容來自半導體(tǐ)行業觀察綜合,謝謝。)

昨天,證監會發布創業闆上市審議結果,國産EDA廠商(shāng)華大(dà)九天首發符合發行條件、上市條件和信息披露要求,獲得首發通過。

據公司招股說明書(shū),華大(dà)九天主要從事EDA工(gōng)具軟件的開(kāi)發、銷售及相關服務。EDA工(gōng)具是集成電路領域的上遊基礎工(gōng)具,應用于集成電路設計、制造、封裝、測試等産業鏈各個環節,是集成電路産業的戰略基礎支柱之一(yī)。公司主要産品包括模拟電路設計全流程EDA工(gōng)具系統、數字電路設計EDA工(gōng)具、平闆顯示電路設計全流程EDA工(gōng)具系統和晶圓制造EDA工(gōng)具等EDA工(gōng)具軟件,并圍繞相關領域提供技術開(kāi)發服務。公司相關産品和服務主要應用于集成電路設計及制造領域。

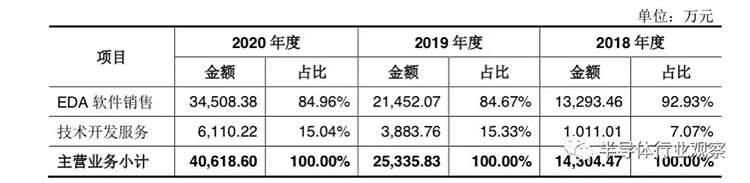

報告期内,公司主營業務收入構成情況如下(xià):

統計顯示,報告期内,公司營業收入與歸屬母公司所有者淨利潤均呈快速增長趨勢。其中(zhōng)營業收入分(fēn)别爲15,078.20萬元、25,722.00萬元和41,480.22萬元,2019年較上年同比增長70.59%,2020年較上年同比增長61.26%;歸屬母公司所有者的淨利潤分(fēn)别爲4,851.94萬元、5,715.77萬元和10,355.87萬元,2019年較上年同比增長17.80%,2020年較上年同比增長81.18%。

關于股東方面,在2020年7月6,九天有限公司增資(zī)完成後,具體(tǐ)股東情況如下(xià)所示。

具體(tǐ)到産品方面,華大(dà)九天提供了以下(xià)産品:

(1)公司EDA工(gōng)具軟件産品情況

①模拟電路設計全流程EDA工(gōng)具系統

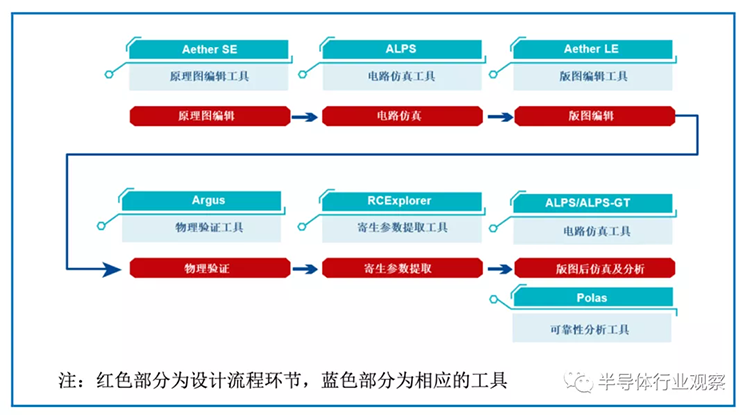

模拟集成電路設計是指對模拟電路進行結構設計、版圖設計、功能和物(wù)理驗證的全過程。這一(yī)過程包括原理圖編輯、電路仿真、版圖編輯、物(wù)理驗證、寄生(shēng)參數提取、可靠性分(fēn)析等環節。

模拟電路的設計從原理圖設計開(kāi)始。原理圖包含抽象化的器件符号及連線,這些符号表示晶體(tǐ)管、電阻、電容等。爲了确保電路工(gōng)作正确,設計師需要用到電路仿真工(gōng)具以模拟電路的功能、性能等,設計師根據仿真的結果不斷優化電路設計。仿真環節使設計師不用将電路真正制造出來去(qù)檢查電路是否正确,節省了大(dà)量的時間和成本。

此後,芯片設計進入版圖設計環節。版圖設計主要包括版圖的布局和布線,通過版圖設計工(gōng)具将每個器件放(fàng)置到合适位置,并用圖形将各個器件進行正确的連接。版圖設計完成後,需進行物(wù)理驗證,以确保版圖與原理圖一(yī)緻并且符合晶圓制造的要求。由于器件、金屬線等都存在寄生(shēng)電阻和電容,這些電阻電容會對電路的實際工(gōng)作産生(shēng)影響。因此完成物(wù)理驗證後,還需對版圖進行寄生(shēng)參數提取,産生(shēng)包含寄生(shēng)參數的後仿真電路網表,并通過後仿真來驗證電路實際工(gōng)作的各項功能和性能。

此外(wài),由于壓降的存在會直接影響器件的工(gōng)作性能,而電流密度局部過大(dà)會導緻金屬連線和器件工(gōng)作失效。因此除了以上的各項驗證環節外(wài),壓降和電流密度等可靠性分(fēn)析也是模拟電路設計必不可少的驗證環節。上述模拟電路設計全過程的各個環節都需要使用EDA工(gōng)具。公司是我(wǒ)(wǒ)國唯一(yī)能夠提供模拟電路設計全流程EDA工(gōng)具系統的本土EDA企業。該EDA工(gōng)具系統包括原理圖編輯工(gōng)具、版圖編輯工(gōng)具、電路仿真工(gōng)具、物(wù)理驗證工(gōng)具、寄生(shēng)參數提取工(gōng)具和可靠性分(fēn)析工(gōng)具等,爲用戶提供了從電路到版圖、從設計到驗證的一(yī)站式完整解決方案。該模拟電路設計全流程EDA工(gōng)具系統具體(tǐ)如下(xià)圖所示:

公司模拟電路設計全流程EDA工(gōng)具系統主要客戶群體(tǐ)爲集成電路設計企業,包括從事模拟芯片設計和大(dà)規模系統級芯片設計的企業,主要用于模拟芯片和系統級芯片中(zhōng)模拟電路模塊的設計和驗證。模拟芯片主要包括電源管理類芯片和信号鏈芯片。電源管理芯片是在電子設備系統中(zhōng)擔負起對電能的變換、分(fēn)配、檢測及其他電能管理職責的芯片,在不同産品應用中(zhōng)發揮不同的電壓、電流管理功能,需要針對不同的應用采用不同的電路設計。信号鏈芯片是系統中(zhōng)信号從輸入到輸出路徑中(zhōng)使用的芯片,包括信号的采集、放(fàng)大(dà)、傳輸、處理等功能。系統級芯片包括網絡芯片、智能手機處理器芯片等,這些芯片中(zhōng)也包含電源控制、數模轉換等模拟設計模塊。模拟芯片和系統級芯片被廣泛應用于計算機、網絡通訊、數據中(zhōng)心、照明、家用電器、智能家居、消費(fèi)類電子等領域。

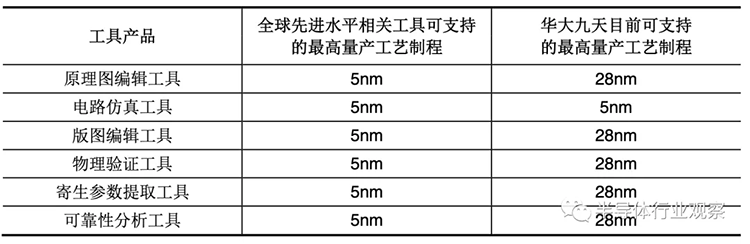

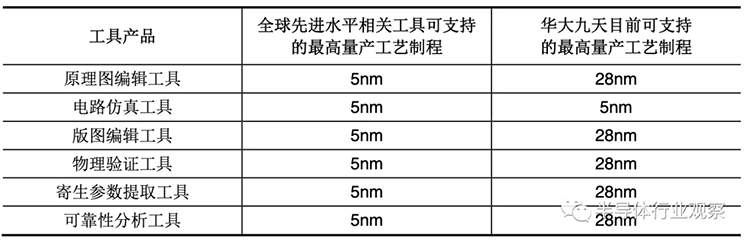

公司目前既有模拟電路設計全流程EDA工(gōng)具系統可支持的集成電路工(gōng)藝制程具體(tǐ)情況如下(xià)表所示:

根據上表,公司目前主要既有模拟電路設計全流程EDA工(gōng)具系統中(zhōng),電路仿真工(gōng)具支持最先進的5nm量産工(gōng)藝制程,處于國際領先水平;其他模拟電路設計EDA工(gōng)具支持28nm工(gōng)藝制程,與已支持5nm先進工(gōng)藝的同類領先工(gōng)具仍存在一(yī)定差距。因此,發行人模拟電路設計全流程EDA工(gōng)具系統中(zhōng)部分(fēn)工(gōng)具達到國際領先水平,但整體(tǐ)尚未支持16nm及以下(xià)先進工(gōng)藝制程。

模拟芯片具有生(shēng)命周期長、對先進工(gōng)藝制程依賴低的特點,更關注性能指标、可靠性和成本,因此通常采用更穩定的成熟工(gōng)藝制程。目前大(dà)部分(fēn)模拟芯片産品仍在使用28nm及以上的成熟工(gōng)藝制程。因此,從工(gōng)藝支持角度講公司既有模拟電路設計及驗證工(gōng)具已可以滿足大(dà)部分(fēn)模拟設計客戶的制程需要。此外(wài),公司本次募投項目中(zhōng)的“模拟設計及驗證EDA工(gōng)具升級”等項目亦着眼于模拟電路設計領域綜合技術水平的提升,将進一(yī)步促進公司産品支持更高水平的工(gōng)藝制程。

此外(wài),除工(gōng)藝制程外(wài),衡量EDA工(gōng)具技術水平的标準還包括功能完備性、可靠性和應對複雜(zá)使用環境的适應性等。在特定工(gōng)藝制程上,針對上述标準的提升也是EDA工(gōng)具先進性的重要體(tǐ)現。

②數字電路設計EDA工(gōng)具

數字電路設計是指電路功能設計、邏輯綜合、物(wù)理實現以及電路和版圖分(fēn)析驗證的過程。這一(yī)過程通常分(fēn)爲數字前端和數字後端兩部分(fēn),主要包括單元庫準備、邏輯仿真、邏輯綜合、布局布線、寄生(shēng)參數提取、時序分(fēn)析與優化、物(wù)理驗證和版圖集成與分(fēn)析等環節。

數字前端設計流程從設計架構開(kāi)始,用硬件語言對芯片功能進行描述編碼;通過仿真工(gōng)具進行邏輯仿真,檢驗設計代碼的正确性;然後通過邏輯綜合将設計代碼映射到電路結構,輸出描述數字電路結構的電路網表文件。

數字後端設計流程負責将前端設計生(shēng)成的電路網表實現爲可生(shēng)産的物(wù)理版圖。通過布局布線工(gōng)具将電路網表中(zhōng)使用到的各種單元和IP在版圖上進行合理擺放(fàng)、連接,形成布局布線後的電路網表和版圖;對布局布線後的版圖進行寄生(shēng)參數提取,再進行時序分(fēn)析和優化、物(wù)理驗證等工(gōng)作,确認設計不存在功能和物(wù)理規則上的問題;最後進行版圖集成,形成最終交付晶圓代工(gōng)廠生(shēng)産的版圖。

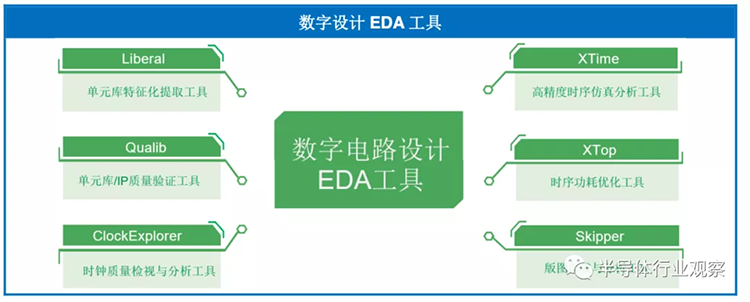

上述過程的各個環節都需要相應的EDA工(gōng)具。公司的數字電路設計EDA工(gōng)具爲數字電路設計的部分(fēn)環節提供了特色解決方案,具體(tǐ)包括單元庫特征化提取工(gōng)具Liberal、單元庫/IP質量驗證工(gōng)具Qualib、時序仿真分(fēn)析工(gōng)具XTime、時序功耗優化工(gōng)具XTop以及版圖集成與分(fēn)析工(gōng)具Skipper等。主要工(gōng)具如下(xià)圖所示:

公司目前既有數字電路設計EDA工(gōng)具可支持的集成電路工(gōng)藝制程具體(tǐ)情況如下(xià)表所示:

根據上表,公司目前已發布的數字電路設計EDA工(gōng)具中(zhōng),單元庫/IP質量驗證工(gōng)具、高精度時序仿真分(fēn)析工(gōng)具、時序功耗優化工(gōng)具、版圖集成與分(fēn)析工(gōng)具和時鍾質量檢視與分(fēn)析工(gōng)具均可支持目前國際最先進的5nm量産工(gōng)藝制程,處于國際領先水平;單元庫特征化提取工(gōng)具開(kāi)發完成時間較短,目前可支持40nm量産工(gōng)藝制程,與同類國際領先工(gōng)具仍存在一(yī)定差距。整體(tǐ)來看,公司已發布的數字電路設計EDA工(gōng)具中(zhōng),除個别工(gōng)具外(wài)均達到國際領先水平,可支持5nm量産工(gōng)藝制程。

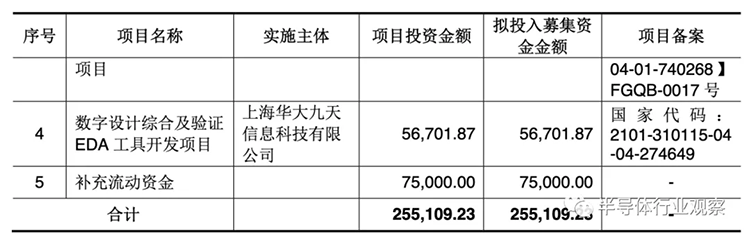

此外(wài),公司目前在數字電路EDA領域僅覆蓋數字電路設計的部分(fēn)流程,尚未實現全流程工(gōng)具覆蓋,公司本次募投項目中(zhōng)的“電路仿真及數字分(fēn)析優化EDA工(gōng)具升級項目”和“數字設計綜合及驗證EDA工(gōng)具開(kāi)發項目”等亦着眼于提升數字電路設計領域EDA工(gōng)具的覆蓋完整率,并将進一(yī)步促進對更高水平工(gōng)藝制程的支持,從而提升公司在數字電路EDA領域的綜合競争水平。

③平闆顯示電路設計全流程

EDA工(gōng)具系統平闆顯示電路設計與模拟電路的設計理念、設計過程和設計原則有一(yī)定的相似性。公司在已有模拟電路設計工(gōng)具的基礎上,結合平闆顯示電路設計的特點,開(kāi)發了全球領先的平闆顯示電路設計全流程EDA工(gōng)具系統。

該EDA工(gōng)具系統包含平闆顯示電路設計器件模型提取工(gōng)具、平闆顯示電路設計原理圖編輯工(gōng)具、平闆顯示電路設計版圖編輯工(gōng)具、平闆顯示電路設計電路仿真工(gōng)具、平闆顯示電路設計物(wù)理驗證工(gōng)具、平闆顯示電路設計寄生(shēng)參數提取工(gōng)具和平闆顯示電路設計可靠性分(fēn)析工(gōng)具等。以上工(gōng)具被集成在統一(yī)的設計平台中(zhōng),爲設計師提供了一(yī)套從原理圖到版圖,從設計到驗證的一(yī)站式解決方案,爲提高平闆顯示電路設計效率,保證設計質量提供了有力的工(gōng)具支撐。

該EDA工(gōng)具系統具體(tǐ)如下(xià)圖所示:

④晶圓制造EDA工(gōng)具

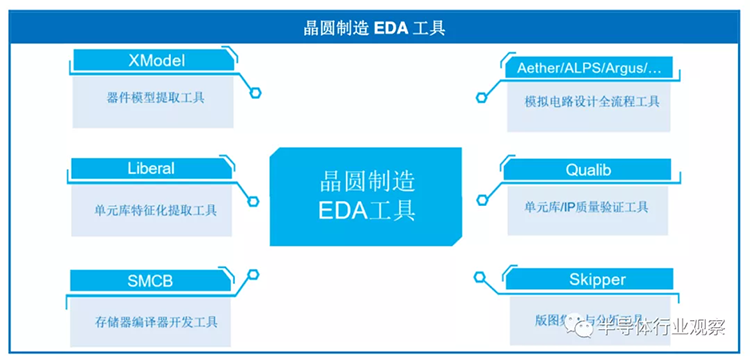

公司針對晶圓制造廠的工(gōng)藝開(kāi)發和IP設計需求,提供了相關的晶圓制造EDA工(gōng)具,包括器件模型提取工(gōng)具、存儲器編譯器開(kāi)發工(gōng)具、單元庫特征化提取工(gōng)具、單元庫/IP質量驗證工(gōng)具、版圖集成與分(fēn)析工(gōng)具以及模拟電路設計全流程EDA工(gōng)具等,爲晶圓制造廠提供了重要的技術支撐。公司的晶圓制造EDA工(gōng)具具體(tǐ)如下(xià)圖所示:

此外(wài),公司基于在集成電路領域多年的技術積累,建立了完善的自動化設計服務流程,爲集成電路設計和制造客戶提供技術開(kāi)發服務。服務内容主要包括設計支持服務和晶圓制造工(gōng)程服務,主要涉及測試芯片設計、半導體(tǐ)器件測試分(fēn)析、器件模型提取、單元庫設計及存儲器編譯器開(kāi)發服務等。

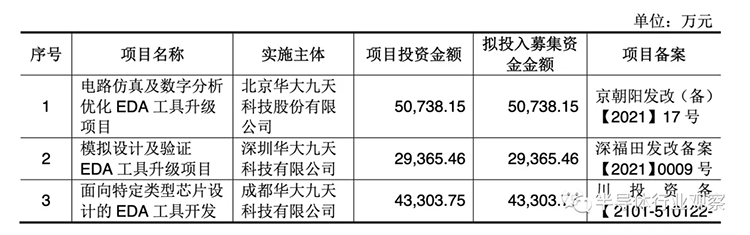

根據招股說明書(shū),公司本次拟向社會公開(kāi)發行股票108,588,354股,占發行後公司總股本的比例爲20%。本次公開(kāi)發行股票所募集的資(zī)金扣除發行費(fèi)用後,将全部用于以下(xià)項目: